技术和能力

T

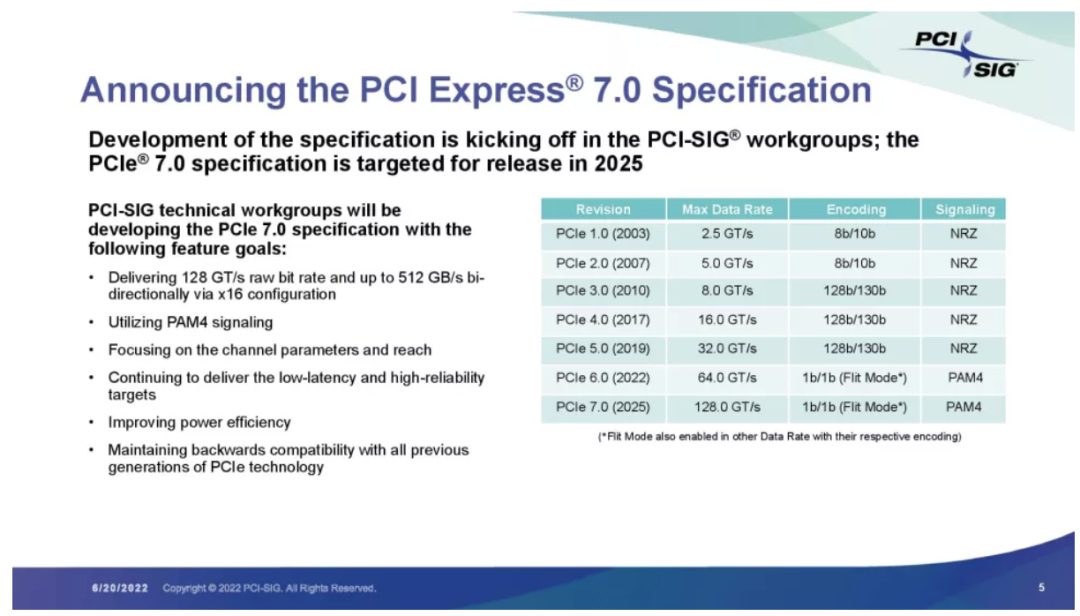

2020年在AMD首发PCIe 4.0后,Intel也于去年开始普及PCIe 5.0并在12代英特尔平台上使用。然而,传输标准的制定却远远领先于产品的研发。日前,正在举行的2022 年 PCI-SIG开发者大会上(PCI-SIG 是 PCIe 接口背后的联盟,这是一个由 900 多家成员公司组成的开放行业标准),PCIe 接口标准委员会PCI-SIG 就公布了PCIe 7.0的规范目标,称其数据速率高达 128 GT/s,并在 2025 年向其成员发布,这相当于在编码开销之前,通过 16 通道 (x16) 连接能实现 512 GB/s 的双向吞吐量。

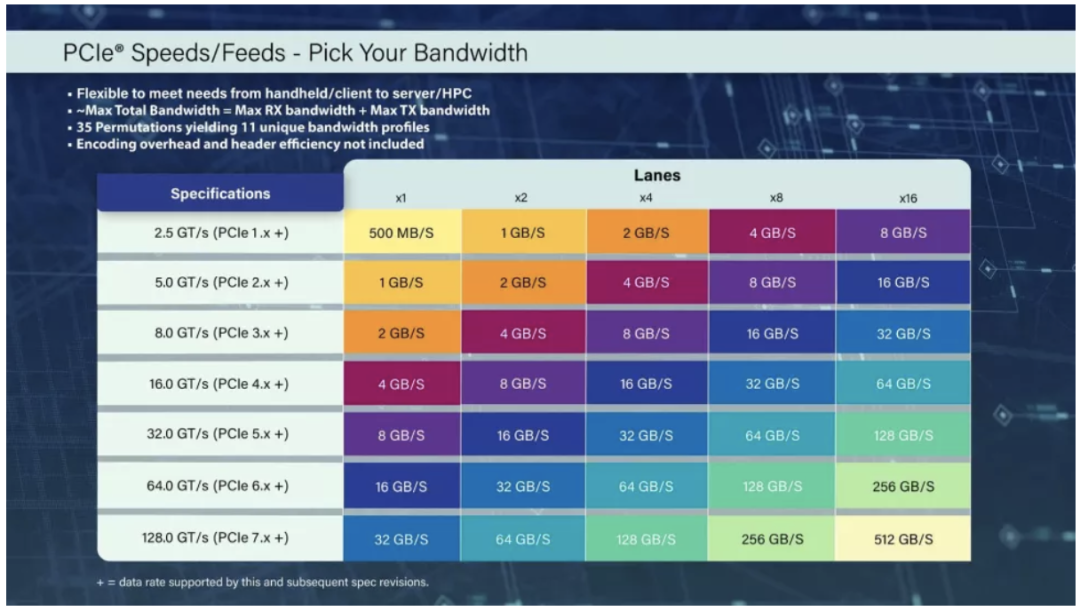

PCI-SIG指出,PCIe 7.0 接口将在x16连接上提供惊人的512 GB/s的双向吞吐量,但这是在编码开销和报头效率的影响之前,这两者都会影响可用带宽。

PCIe 7.0接口将继续使用1b/1b flit模式编码和PCIe 6.0引入的PAM4信号技术,这比3.0至5.0规格使用的128b/130b编码和NRZ信号有明显的改进。因此,实际可用带宽将略低于 512 GB/s,但仍然代表着比PCIe 6.0接口翻了一番。

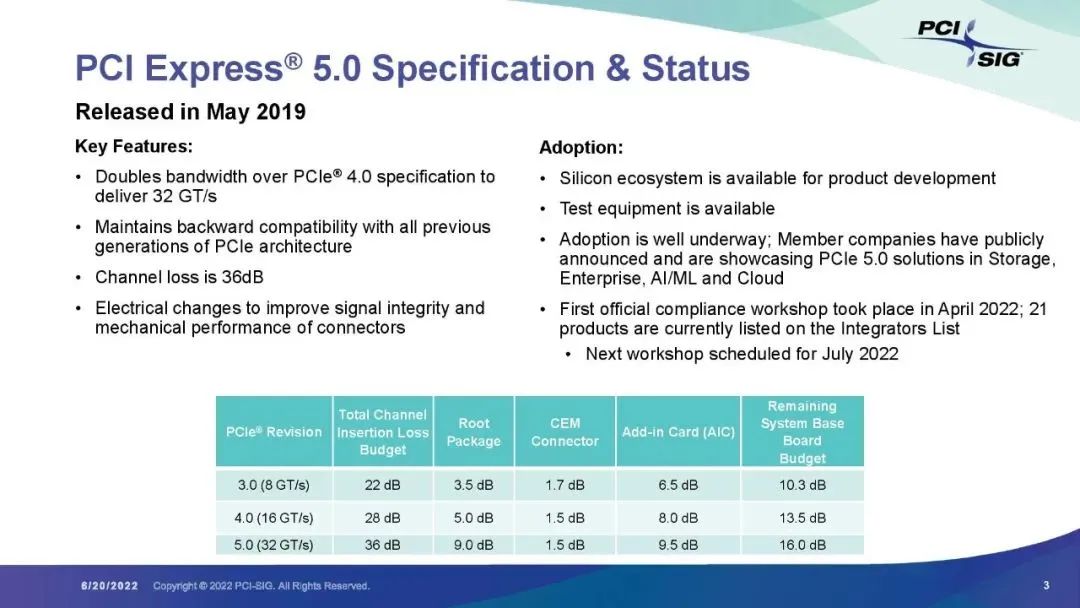

正如我们看到的PCIe 4.0和5.0,由于更快的信令速率,PCIe线路的长度将再次缩短。这意味着在没有额外组件的情况下,PCIe 根设备(如 CPU)和终端设备(如 GPU)之间的最小允许距离将缩短。因此,与前几代接口相比,主板将需要更多的重定时器和由更高质量材料组成的更厚的PCB,而对PCIe 7.0的支持将导致主板价格的再次上涨。

值得注意的是,每条通道的带宽更高,对于现在 x1 连接的双向带宽为 32 GB/s,因此PCIe 7.0 可以让一些设备的连接更 "薄"(例如,使用x4而不是x8连接)。

PCIe 7.0规范的基础工作是在今年早些时候PCI-SIG确定了PCIe 6.0规范之后进行的,它将提供比上一代PCIe 6.0接口多一倍的带宽。瑞萨公司的PCIe 6.0设备在4月份开始进入市场。然而,在我们看到支持这种高速接口的固态硬盘和GPU等设备之前,还需要一些时间—虽然这些规格通常在我们看到出货芯片之前很长时间就已经批准和确定了。

正如你所注意到的,目前市场上即使是PCIe 5.0设备仍然没有多少,尽管该接口确实随着英特尔的Alder Lake进入了主流主板,并且还将出现在今年晚些时候到货的 AMD 即将推出的 Zen 4 Ryzen 7000平台上。首批 PCIe 5.0 SSD 将与 Ryzen 7000 处理器同时上市,但我们已经看到了用于数据中心和 AI/ML 设备的 PCIe 5.0 设备的产品公告。

换句话说,您在相当长的一段时间内都不会在市场上看到 PCIe 7.0 设备,尽管 PCI-SIG 现在开始定义规范并希望实现其每三年发布一个新规范的目标。PCIe 7.0 规范预计将在 2025 年落地,但我们要到 2028 年才能看到终端设备。

PCIe 7.0 规范目标:

通过 x16 配置提供128GT/s的原始比特率和高达512GB/s的双向传输速率

通过 x16 配置提供128GT/s的原始比特率和高达512GB/s的双向传输速率

利用 PAM4调制

利用 PAM4调制

关注渠道参数和覆盖范围

关注渠道参数和覆盖范围

继续提供低延迟和高可靠性的目标

继续提供低延迟和高可靠性的目标

提高电源效率

提高电源效率

保持与所有前几代 PCIe 技术的向后兼容性

保持与所有前几代 PCIe 技术的向后兼容性

*本文转自:高速射频百花潭